Montagetechnologien der Elektronik

Die im Waferprozess der Halbleiterindustrie hergestellten Chips können ihre Funktion nur ausüben, wenn sie zu Bauelementen und/oder Baugruppen komplettiert werden. Dazu sind elektrisch leitende, mechanisch stabile und sehr zuverlässige Kontakte zwischen den Pads der Chips und geeigneten äußeren Anschlüssen (first level interconnects) sowie weiter im Package bzw. auf die nächsten Verbindungsebenen der Baugruppe (second level interconnects) notwendig.

Die Aufbau- und Verbindungstechnik erschließt neben den hauptsächlich angewandten Prozessen des Bondens, Lötens oder Leitklebens auf starren organischen, flexiblen organischen oder anorganischen Substraten ständig neue Anwendungen. Die Diversifizierung der Bauelementeformen, die Weiterentwicklung von Substrat- und Verbindungsmaterialien und spezifische Einsatzbedingungen für Elektronikprodukte bedingen angepasste Technologien. Das Arbeitsgebiet „Montage-Technologien der Elektronik“ widmet sich sowohl der Modifizierung von Standardprozessen als auch der Entwicklung neuer Verfahren.

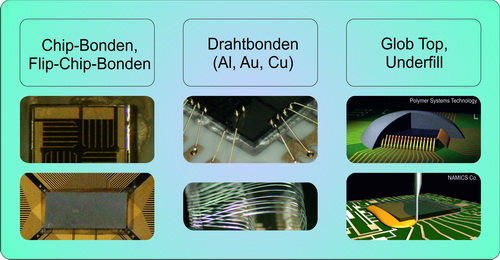

Auf dem First-Level-Interconnect werden gegenwärtig und in absehbarer Zukunft die Ankontaktierungen in mehr als 80% aller Anwendungen durch Chip- und Drahtbonden realisiert. Dabei werden die Chips rückseitig auf ein Substrat oder in ein Gehäuse vollflächig aufgeklebt (Chipbonden). Die Abkontaktierung vom Chip wird durch dünne Mikrodrähte von ≥ 20µm Durchmesser verwirklicht, welche mit den jeweiligen Kontaktflächen verschweißt werden (Drahtbonden).

Alternativ können die Chips mit Hilfe der Flip-Chip-Technologie frontseitig direkt kontaktiert werden. Dazu werden auf den Kontaktflächen der Chips spezielle Bumps appliziert, um einen stabilen und zuverlässigen Kontakt zum Substrat realisieren zu können. Für die Kontaktierung kommen vorwiegend Klebe- oder Löttechnologien zum Einsatz.

Im Arbeitsgebiet Mikroverbindungstechnik werden die Materialien und Prozesse zur Weiterverarbeitung von Halbleiterchips zu Bauelementen/-gruppen betrachtet und charakterisiert mit dem Ziel, die Miniaturisierung voranzutreiben und die Zuverlässigkeit zu erhöhen. Ein besonderer Fokus liegt dabei beim Drahtbonden. Untersucht wird hier die Eignung verschiedenster Drahtwerkstoffe auf unterschiedlichen Metallisierungsschichten.

Durch Anwendung von Nanotechnologien in der Halbleitertechnik steigt der Integrationsgrad der Chips. Dies führt neben vielen anderen Veränderungen zu einer bedeutenden Steigerung der Anzahl der Chipanschlüsse. In Zukunft werden folglich immer kleinere Abmessungen der Pads sowohl auf dem Chip als auch auf dem Substrat oder den Leadframes zur Verfügung stehen. Daraus resultieren extreme Miniaturisierungsanforderungen. Hinsichtlich des Drahtbondens werden diese sowohl den eingesetzten Draht als auch die zu bondenden Schichten bzw. Schichtsysteme verändern. Oberstes Gebot bleibt eine maximale Kontaktzuverlässigkeit, die werkstoffwissenschaftlich auch für extreme Einsatzbedingungen abgesichert und durch stabile Fertigungsprozesse garantiert werden muss. In diese Richtung zielen alle Überlegungen zur Weiterentwicklung der Materialien und Prozesse für die Mikrokontaktierung, die ihren Niederschlag u. a. in einer Roadmap zur Mikroverbindungstechnik gefunden haben, die vom Institut gemeinsam mit der Industrie erarbeitet worden ist.

Die Oberflächenmontage (Surface Mount Technology) muss sich aktuell einer breiten Palette unterschiedlichster Anforderungen stellen. Diese ergeben sich aus den Produktanforderungen, den Einsatzbedingungen der Elektronik und den Zuverlässigkeitsanforderungen. Dies hat unter anderem eine Diversifizierung der Aufbautechnologien zur Folge. Neben den „traditionellen“ Verbindungstechnologien auf Baugruppenebene (Second-Level-Interconnect), dem Löten und Leitkleben, werden Verfahren modifiziert, zum Beispiel das Diffusionslöten, das Löten in Kombination mit Druckvariationen, um homogenere Flächenlötungen an Leistungshalbleitern zu erzielen, aber auch neue Verfahren eingeführt, wie zum Beispiel das Sintern.

Das Diffusionslöten bietet zum Beispiel die Möglichkeit, Verbindungsstellen durch isotherme Erstarrung bei Temperaturen herzustellen, die den üblichen Prozesstemperaturen beim Reflowlöten von SnAgCu-Legierungen im Bereich bis 250°C entsprechen. Gleichzeitig sind solche Verbindungsstellen, eine durchgängige Bildung intermetallischer Phasen vorausgesetzt, nach ihrer Erstarrung bis mindestens über 400°C thermisch belastbar. Dies ist eine wichtige Eigenschaft im Hinblick auf leistungselektronische Baugruppen mit extrem hohen Stromdichten. Allerdings ändert sich damit auch das Zuverlässigkeitsverhalten des Gesamtaufbaus und muss somit völlig neu bewertet werden.